# Freescale Semiconductor, Inc. Application Note

Document Number: AN4963

Rev. 0, 08/2014

## Wearable ECG Patch

by José Santiago López Ramírez

## 1 Introduction

Electronic products are becoming smaller and more power efficient. Portable healthcare devices, specifically those used in fitness and diagnostic medicine, require small and portable microcontrollers that can take continuous measurements for long periods of time with small batteries. Selecting an adequate microcontroller is important for achieving high processing capabilities with the lowest power consumption possible. This application note demonstrates the use of the Kinetis K5x and the Kinetis L series microcontrollers within a wearable ECG patch.

## 2 ECG patch

The ECG patch is a small device that is connected to the body surface (commonly the chest) to process, acquire and transmit the electrical signal of the patient's heart activity. This information is later used for medical diagnostic (Holter monitors) or for displaying parameters such as heart rate in fitness activities.

#### Contents

1 Introduction

| 1.   | miroduction                  | 1 |

|------|------------------------------|---|

| 2.   | ECG patch                    | 1 |

| 3.   | Hardware                     | 2 |

| 3.1. | Amplification and filtering  | 2 |

| 3.2. | Digitalization               | 4 |

| 3.3. | Microcontroller              | 4 |

| 3.4. | Display and transceiver      | 6 |

| 4.   | Software                     | 6 |

| 4.1. | Sampling                     | 7 |

| 4.2. | Processing                   | 8 |

| 5.   | Kinetis K51 demo application | 9 |

| 6.   | References and resources     | 1 |

|      |                              |   |

Hardware

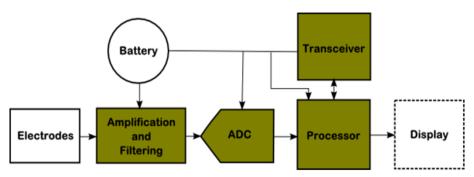

Figure 1. ECG patch concept diagram

Figure 1 shows the general concept for an ECG patch. At least three electrodes are in contact with the patient's skin, creating an ECG lead vector across the heart. The ECG signal is amplified and filtered in the first analog processing stage. The signal is acquired by the microcontroller using an embedded ADC and processed using digital filtering algorithms. The firmware can include the necessary algorithms for heart rate calculation. The final information can be transmitted wirelessly or shown on an embedded display.

### 3 Hardware

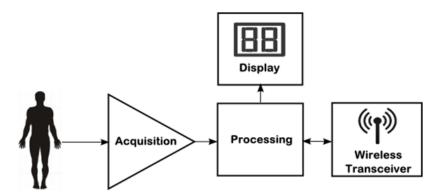

The ECG patch application is composed of three important stages; Acquisition, Processing and Display/Transmission. A block diagram with the hardware stages required is shown in Figure 2.

Figure 2. Hardware block diagram

## 3.1 Amplification and filtering

The ECG signal is acquired from the body using at least three electrodes; two that create a differential pair and one that is used as reference. The amplitude of this signal goes from hundreds of microvolts up to 5 or 10 millivolts. A preamplifier is required to elevate this voltage to levels that can be treated properly for noise reduction.

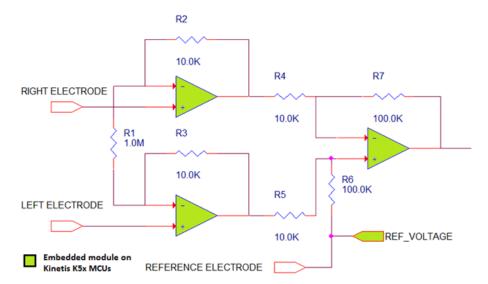

Figure 3. Instrumentation amplifier schematic

Figure 3 shows the schematic diagram of an instrumentation amplifier. These circuits are preferred as preamplifiers due the high gains they can achieve and their high common mode rejection ratio (CMRR). This circuit requires three operational amplifiers and seven resistors. A reference voltage source is required when the circuit works with a single power supply to create a virtual ground necessary to translate the negative voltages to the positive voltage domain.

The pre-amplified signal must be passed through a band-pass filter with a window from 0.5 Hz to 150 Hz. This filter removes the high frequency noise from the signal as well as the baseline variations. Analog filters of order 3 or 4 are suggested for this application, however lower order filters can be used when complemented with digital signal processing. This enables bill of materials (BOM) and overall circuit cost reduction.

Even when the ECG patch is powered by batteries, it is recommended to include a band-reject filter with a window from 50 Hz to 60 Hz to remove the electric line induction noise.

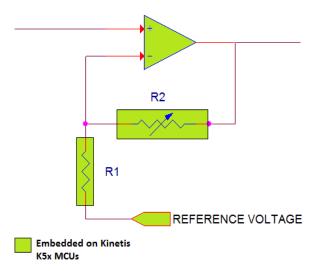

An additional amplifier can be added after the filtering stage and used for gain control. Figure 4 shows the schematic circuit used for the second amplifier. Automatic gain control algorithms can be implemented using an amplifier with programmable gain. This is particularly useful in fitness heart rate detection devices where the signal amplitude varies among each user and preserving the original amplitude is not crucial.

Hardware

Figure 4. Second stage amplifier

## 3.2 Digitalization

After the signal has been amplified and filtered, it must be converted to digital values in order to be processed and transmitted by the microcontroller. Digitalization is performed using an analog-to-digital converter (ADC). The signal is sampled with an adequate frequency and temporarily stored in memory for future processing. The sample frequency depends on the specific application. Heart rate counters will require lower sample frequencies while ECG monitors require higher rates.

A 12-bit ADC resolution is sufficient for ECG monitoring applications. Nevertheless, a higher resolution provides a better detail in the signal observed.

#### 3.3 Microcontroller

When selecting a microcontroller for ECG patch applications, two important factors must be taken into consideration; the device is small in size, and is portable by using battery power. The selected device must also operate with low-power. Additional features such as high analog integration and the capability to execute DSP instructions contribute to reduction in size and power consumption.

Freescale offers two separate microcontroller families that provide these required features, the Kinetis K5x and the Kinetis L series.

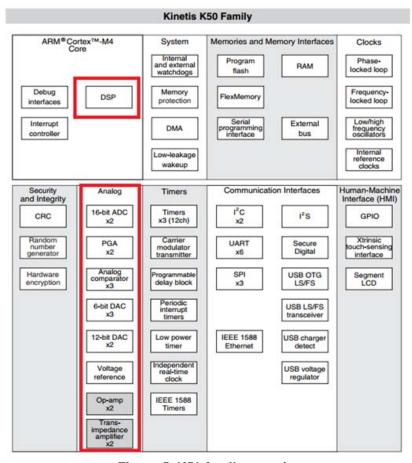

#### 3.3.1 Kinetis K5x series

The Kinetis K5x series is a low-power, analog-integrated family of microcontrollers. This family has an ARM® Cortex®-M4 core which includes DSP instructions that facilitate signal processing tasks. It also features a complete analog measurement engine that includes embedded ADC, DAC, OpAmps, and reference voltage generator among other modules that can considerably reduce the board size and BOM cost of the design.

Figure 5. K50 family overview

#### 3.3.2 Kinetis L

Kinetis L series microcontrollers combine the energy-efficiency and ease-of-use of the ARM Cortex-M0+ processor with the performance, peripheral sets, enablement, and scalability of the Kinetis 32-bit MCU portfolio.

Kinetis L series MCUs are also hardware and software compatible with the ARM Cortex-M4-based Kinetis K series, providing a scalable migration path to more performance, memory and feature integration.

Software

#### Kinetis L Series MCU Families

| Common Features                                              | Optional Features |                     |            |           |              |     |          |        |        |        |     |     |

|--------------------------------------------------------------|-------------------|---------------------|------------|-----------|--------------|-----|----------|--------|--------|--------|-----|-----|

|                                                              |                   |                     |            |           | Key Features |     |          |        |        |        |     |     |

| System                                                       | Family            | Flash               | SRAM       | Pin Count | USB          | Seg | DMA      | LLWU   | ADC    | DAC    | PS  | TSI |

| ARM® Cortex™-M0+ core, 48 MHz                                |                   |                     |            |           | OTG          | LCD | Dillo (  | LLIIIO | 7.00   | Brito  |     |     |

| Multiple low power modes and<br>peripherals, low-power boot, | KL46              | 128-256 KB          | 16-32 KB   | 64-121    | 1            | ,   | 1        | 1      | 16-bit | 12-bit | - 1 | - 1 |

| clock gating                                                 | KL40              | 120-230 ND          | 10-32 NB   | 04-121    | <b>V</b>     | 1   | 1        | 1      | 10-Dit | 12-DIL | 1   | 1   |

| 1.71–3.6 V. –40° C to +105° C ™                              | KL36              | 64-256 KB           | 8-32 KB    | 64-121    |              | 1   | 1        | J      | 16-bit | 12-bit | 1   | 1   |

| 111 0.0 1, 40 0 10 1100 0                                    | KEGO              | 01-20010            | 0-02 100   | 04-121    |              | V   | ٧        | ٧      | 10-01  | 12-011 | ٧   | ٧   |

| Memory                                                       | KL34              | 64 KB               | 8 KB       | 64-00     |              | ↓   | 1        | 1      | 12-bit |        |     |     |

| 90 nm TFS flash, SRAM                                        |                   |                     |            |           |              |     |          |        |        |        |     | =   |

| Internal memory security/protection                          | KL26              | 32-256 KB           | 4-32 KB    | 32-121    | 1            |     | 1        | 1      | 16-bit | 12-bit | 1   | 1   |

|                                                              | KL25              | 32-128 KB           | 4-16 KB    | 32-80     | 1            |     | 1        | J      | 16-bit | 12-bit |     | 1   |

| Analog Peripherals                                           |                   |                     |            |           | _            |     | <u> </u> | -      |        | 12 211 |     | -   |

| 12/16-bit ADC, 12-bit DAC                                    | KL24              | 32-64 KB            | 4-8 KB     | 32-80     | 1            |     | √        | 1      | 12-bit |        |     |     |

| High-speed comparator                                        |                   |                     |            |           |              |     |          |        |        |        |     | _   |

|                                                              | KL16              | 32-256 KB           | 4-32 KB    | 32-64     |              |     | ↓        | 1      | 16-bit | 12-bit | ↓   | ↓   |

| Serial Interfaces                                            | KL15              | 32-128 KB           | 4-16 KB    | 32-80     |              |     | 1        | J      | 16-bit | 12-bit |     | J   |

| UART (including 1 LPUART)                                    | KEIO              | 02 120 110          | 4 10 10    | 00 00     |              | _   | V        | V      | 10.01  | 76 611 |     | V   |

| SPI, PC                                                      | KL14              | 32-64 KB            | 4-8 KB     | 32-80     |              |     | 1        | 1      | 12-bit |        |     |     |

| _                                                            |                   |                     |            |           |              |     |          |        |        |        |     | _   |

| Timers                                                       | KL05              | 8-32 KB             | 1-4 KB     | 24-48     |              |     | √        | √      | 12-bit | 12-bit |     | ↓   |

| Real-time clock PI                                           | KL04              | 8-32 KB             | 1-4 KB     | 24-48     |              |     | 1        | J      | 12-bit |        |     |     |

| 16-bit low-power TPMs                                        |                   |                     | 1 4100     |           |              |     | · •      | · ·    | 16 011 |        |     |     |

| (GP timer/PWM)                                               | KL02              | 8-32 KB             | 1-4 KB     | 16-32     |              |     |          |        | 12-bit |        |     |     |

| Low-power timers                                             | [1] Easture o     | ot available on CS  | D nacksone |           |              |     |          |        |        |        |     |     |

| 32-bit periodic interrupt timer                              |                   | , use software to s |            |           |              |     |          |        |        |        |     |     |

Figure 6. Kinetis L series MCU families

## 3.4 Display and transceiver

When the signal has been acquired and processed by the microcontroller, it can be now transmitted or displayed. Different transceivers can be used for this purpose. Some of the most popular technologies include ZigBee®, Bluetooth® Low Energy (BLE), and Near Field Communication (NFC). When selecting a transceiver for the application, the following points need to be considered:

- · Efficient use of power

- Contained within a small footprint

- Meet the product's communication requirements

For example, BLE can be more suitable for fitness application because of its compatibility with the newest smartphones.

When the information (for example, heart rate) is being displayed in the same device, LCD screens are recommended due their low-power consumption. An embedded LCD controller within the MCU can save important space in the PCB and improve power consumption.

## 4 Software

When the signal has been acquired and pre-processed using analog circuitry, the microcontroller is now responsible for that information to be properly processed, stored and transmitted.

## 4.1 Sampling

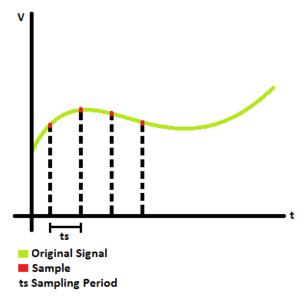

Because of core speed and memory restrictions in microcontrollers, a continuous analog ECG signal cannot be digitally stored and transmitted. Instead, the original signal is separated into parts that are captured and stored for a determined amount of time in a process called sampling.

Figure 7. Sampling

Sampling is defined as the conversion process from a continuous signal to a discrete signal. The discrete signal is a sequence of quantities (samples) taken over a determined period of time (sampling period) that can be stored, processed and used to restore the original signal.

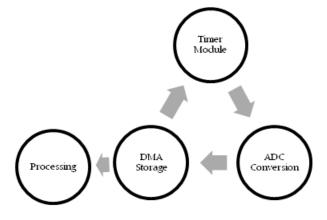

The sampling period is a known parameter when processing and reconstructing the original signal. For that reason this parameter must be as exact as possible when taking samples using the ADC. Using dedicated timers to directly trigger the ADC conversion improves the sampling time accuracy (Figure 8).

Figure 8. Sampling process

Software

#### 4.2 Processing

After the signal has been sampled, it can either be transmitted as is to be processed and analyzed by other microprocessors or be handled by the same MCU. When possible, it is preferable to perform the processing using the same microcontroller. Some of the signal treatment methods are explained below.

#### 4.2.1 Digital filtering

Unlike analog filtering, higher order filters can be implemented digitally without additional circuitry. Digital filters can improve the signal quality by removing undesired frequencies only by performing mathematical operations. The main limitation is the microcontroller's architecture. Increasing the filter order represents a higher processing time and power consumption. The integration of digital signal processor (DSP) instructions in the microcontroller can significantly reduce the processing time for these algorithms.

There are two ways in which a digital filter can be implemented. The first is by convolution (a.k.a. finite impulse response or FIR), and the second is by recursion (a.k.a. infinite impulse response or IIR). Each implementation requires an algorithm to use previously calculated coefficients and filter the input signal.

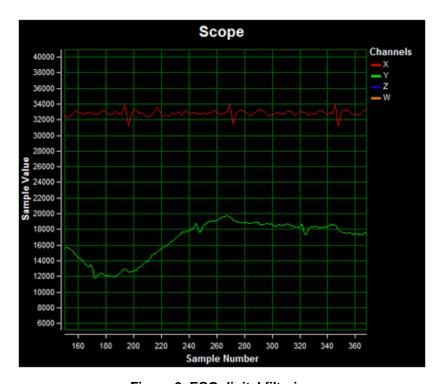

Figure 9. ECG digital filtering

Figure 9 shows an ECG signal (green) being processed using a high-pass FIR filter. The cut-off frequency of this filter was calculated to remove the baseline variations. The result is the processed signal (red) which lacks of the baseline variations. An offset was intentionally added to the result signal to show both signals simultaneously.

#### 4.2.2 QRS complex detection

For applications involving ECG acquisition, the detection of QRS complex is an important matter when determining the heart rate value. This complex represents the electrical activity of the heart during ventricular depolarization and the period between these events is typically used to calculate the heart rate.

Several QRS complex detection algorithms exist. Some are based on detecting the characteristic slope of the QRS complex. Some others determine threshold values for the QR peak or the RS valley. One particular method enables isolating the QRS complex from the remaining signal.

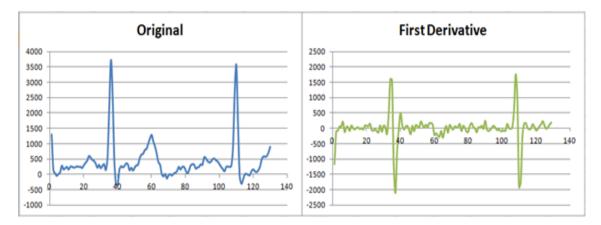

The derivative method consists of subtracting the previous ECG sample to the actual sample. This simple algorithm highlights the fast changes in the signal making them protrude from the rest of the signal. The QRS complexes can be then highlighted using this algorithm.

Figure 10. Derivative method

Figure 10 is an application example of the derivative method. The original signal (blue) is processed. The result signal (green) highlights the QRS complexes and reduces the amplitude of the P and T segments.

## 4.2.3 Heart rate calculation algorithm

Determining a user's heart rate is one of the most common tasks performed by fitness monitors that use ECG. An easy way to do this is to set threshold values that enables detection when a QRS complex is present.

The limitation of this method is the possibility of detecting the P or T complexes. The derivative method explained in the previous chapter can improve the accuracy of the threshold algorithm.

When the QRS complexes can be detected accurately, the heart rate calculation is a simple task that consists of measuring the period between QRS complexes. The inverse of this value is the quantity of beats in a second; 60 times this factor is the quantity of beats per minute (heart rate).

## 5 Kinetis K51 demo application

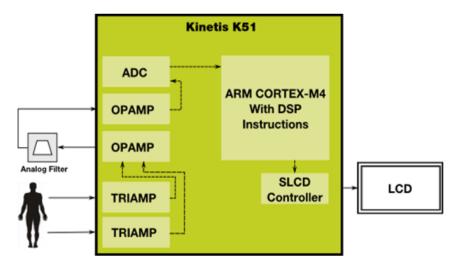

An application example was performed using the Kinetis K51, a low-power, highly analog integrated microcontroller. It implements a basic heart rate monitor using minimal external hardware. Figure 11 shows the high level implementation.

#### Kinetis K51 demo application

Figure 11. Heart rate monitor implementation on Kinetis K51

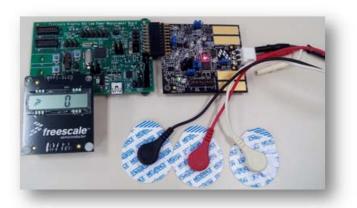

The signal is acquired using the MED-EKG3,5 and the medical low-power board (LPB)4. The MED-EKG is an electrocardiography development board part of the healthcare AFE reference platform. It enables rapid design of ECG based applications.

The LPB is an efficient hardware implementation for Kinetis K60, K51 100 MHz and K51 72 MHz microcontrollers. It includes the minimum hardware needed for low-power implementation.

In addition to these boards, a segment LCD is connected to the LPB for heart rate display. Figure 12 shows the assembled system.

Figure 12. Complete ECG patch set

Patch electrodes are placed in the chest and connected using wires to the MED-EKG board emulating the acquisition system of a wearable patch. The SLCD screen updates the heart rate value every second (Figure 13).

Figure 13. Functioning system

#### 6 References and resources

- 1. Medical Instrumentation Application and Design, John G. Webster.

- 2. The Scientist and Engineer's Guide to Digital Signal Processing, Steven W. Smith.

- 3. More information about Kinetis products and the MED-EKG board can be found at freescale.com.

- 4. Low-power board is not available for sale. Contact a Freescale sales representative if you require a demonstration.

- 5. ECG development is described in AN4323. This document can be found in freescale.com/medical.

- 6. Firmware for this application note was developed using CodeWarrior 10.5 and can be downloaded from freescale.com/codewarrior.

How to Reach Us:

Home Page: freescale.com

Web Support:

freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Registered trademarks: Freescale, the Freescale logo, CodeWarrior, the Energy Efficient Solutions logo and Kinetis are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. ARM and Cortex are the registered trademakers of ARM Limited.

All other product or service names are the property of their respective owners.

© 2014 Freescale Semiconductor, Inc.

Document Number: AN4963

Rev. 0 08/2014