## **DSP56800 to DSP56800E**

## Porting Guide

Digital Signal Controllers

DSP56800ERG Rev. 1.1 11/2005

freescale.com

## **Contents**

#### **Chapter 1** Introduction **Chapter 2 Quick Reference** 2.1 2.1.1 2.1.2 2.1.3 2.1.4 2.2 **Chapter 3 Comparing the Two Architectures** 3.2 3.3 3.3.1 3.3.2 Chapter 4 AGU Registers 4.1 4.2 Issues with AGU Arithmetic......4-2 4.2.1 Cases Solved by Legacy Instructions—Linear Addressing . . . . . . . . . . . . . . . . . 4-3 4.2.2 4.2.3 Cases Solved by Adding a Zero-Extend Instruction..... 4-4 4.2.4 **Chapter 5 Compatibility Issues** 5.1 5.2 5.3 5.4 5.4.1 5.4.2 5.4.3 Extending the Reach on Change-of-Flow Instructions...... 5-6

5.4.4

5.4.5

| 5.5    | Changes Related to the I/O Short Addressing Mode |        |

|--------|--------------------------------------------------|--------|

| 5.6    | Strategy for Loading AGU Registers               | 5-8    |

| 5.7    | Requirements for {R0-R3, N}                      | 5-9    |

| 5.7.1  | As Pointer Registers                             | 5-9    |

| 5.7.2  | As Offset Registers                              | 5-9    |

| 5.8    | Reading the LC Register                          | . 5-10 |

| 5.9    | Numeric Target References                        | . 5-10 |

| 5.10   | Hardware Loop Restrictions                       | . 5-11 |

| 5.10.1 | Restrictions Common to DO and REP                | . 5-11 |

| 5.10.2 | Restrictions Specific To REP                     | . 5-11 |

| 5.10.3 | Restrictions Specific To The DO Instruction      | . 5-12 |

| 5.11   | Differences when Saturation is Enabled           | . 5-12 |

| 5.12   | Computing the Zero Condition Code                | . 5-14 |

| 5.13   | Computing the Carry Condition Code               | . 5-14 |

| 5.14   | New Requirements for X/P Mode                    | . 5-14 |

| 5.14.1 | Entering X/P Mode                                | . 5-14 |

| 5.14.2 | Exiting X/P Mode                                 |        |

| 5.15   | Unsupported DSP56800 Instruction Syntax          |        |

| 5.16   | Requirements on Context Save/Restore             |        |

| 5.17   | Legacy Programs Larger than 64K                  |        |

| 5.18   | Compatibility Issues at the Chip Level           |        |

| 5.18.1 | Interrupt Priority Level                         |        |

| 5.18.2 | Interrupt Vector Locations                       |        |

| 5.18.3 | Peripheral Space Locations                       |        |

| 5.18.4 | Dual Read Instruction                            |        |

| 5.18.5 | The OMR EX Bit                                   |        |

| 5.19   | Delay on Interrupt Enable and Disable            |        |

| 5.19.1 | Enabling Interrupts — CCPL set to "0"            |        |

| 5.19.2 | Disabling Interrupts — CCPL set to "3"           | . 5-24 |

| Chap   |                                                  |        |

| Optin  | nizing Legacy Code                               |        |

| Appe   | ndix A                                           |        |

| irans  | slation Tables                                   |        |

| A.1    | Register Field Notation                          | A-1    |

| A.1.1  | DSP56800 Register Field Notation                 | A-1    |

| A.1.2  | DSP56800E Register Field Notation                |        |

| A.1.3  | Immediate Value Notation                         | A-6    |

| A.2    | Instruction Mapping Tables                       | A-6    |

| A.3    | Legacy Instruction Summary Tables                |        |

| A.4    | DSP56800 Instruction Aliases                     |        |

| A.4.1  | LSLL Instruction Alias                           | . A-25 |

| A.4.2  | ASL Instruction Alias                            | . A-26 |

| A.4.3  | CLR Instruction Alias                            |        |

| A.4.4  | POP Instruction Alias                            | . A-26 |

|        |                                                  |        |

## **List of Figures**

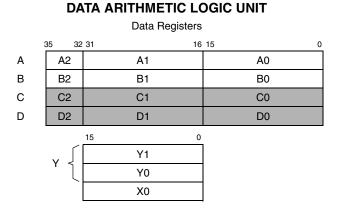

| Figure 3-1 | Programming Model—DSP56800 vs DSP56800E | 3-3 |

|------------|-----------------------------------------|-----|

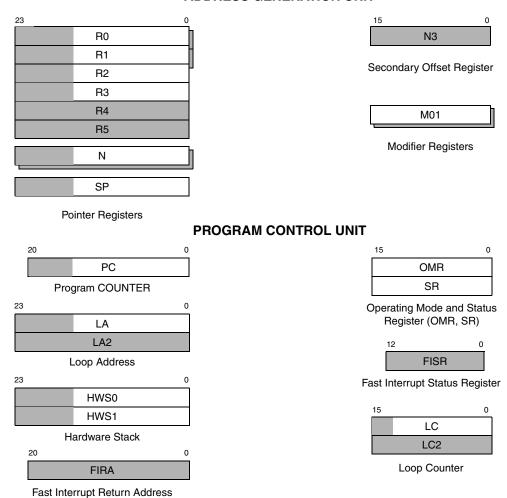

| Figure 3-2 | DSP56800 Memory Spaces                  | 3-4 |

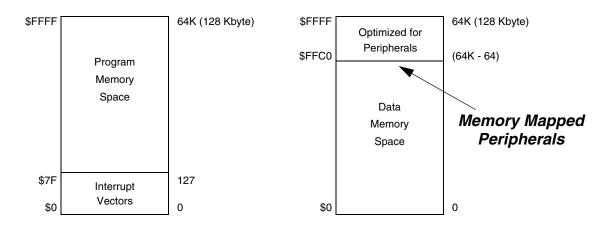

| Figure 3-3 | DSP56800E Memory Spaces                 | 3-5 |

## **List of Tables**

| Table 2-1  | Cases With User-Intervention Requirements                      | 2-1  |

|------------|----------------------------------------------------------------|------|

| Table 2-2  | Uncommon Cases - May Require User-Intervention                 | 2-4  |

| Table 2-3  | Other Cases—No User-Intervention Required                      |      |

| Table 2-4  | Mixed DSP56800 & DSP56800E Syntax                              | 2-7  |

| Table 3-1  | Size of Memory Spaces                                          | 3-4  |

| Table 4-1  | Demonstrating DSP56800 AGU Overflow and Underflow              | 4-2  |

| Table 5-1  | Mapping the DSP56800 Interrupt Levels to the DSP56800E         | 5-21 |

| Table 5-2  | Interrupt Mask Bit Definition                                  | 5-22 |

| Table A-1  | DSP56800 Register Fields for General Purpose Move Instructions | A-2  |

| Table A-2  | DSP56800 Address Generation Unit (AGU) Registers               | A-2  |

| Table A-3  | DSP56800 Data ALU Registers                                    | A-2  |

| Table A-4  | DSP56800 Additional Register Fields for Move Instructions      | A-3  |

| Table A-5  | DSP56800E Register Fields for General-Purpose Writes and Reads | A-3  |

| Table A-6  | DSP56800E Address Generation Unit (AGU) Registers              | A-4  |

| Table A-7  | DSP56800E Data ALU Registers                                   | A-4  |

| Table A-8  | DSP56800E Additional Register Fields for Move Instructions     |      |

| Table A-9  | Immediate Value Notation                                       | A-6  |

| Table A-10 | Instruction Mapping: DSP56800 to DSP56800E                     | A-8  |

| Table A-11 | Tcc Instruction Mapping: DSP56800 to DSP56800E                 | A-21 |

| Table A-12 | Single Parallel Move Mapping: DSP56800 to DSP56800E            | A-21 |

| Table A-13 | Dual Parallel Read Mapping: DSP56800 to DSP56800E              | A-22 |

| Table A-14 | Instruction Alias Mapping: DSP56800 to DSP56800E               | A-23 |

| Table A-15 | Move Word Instructions — Legacy Code                           | A-24 |

| Table A-16 | Data ALU Arithmetic Instructions — Legacy Code                 | A-24 |

| Table A-17 | AGU Arithmetic Instructions — Legacy Code                      | A-24 |

| Table A-18 | Summary of DSP56800 Instruction Aliases and Mapping            | A-25 |

## **List of Code Examples**

| Code Example 4-1  | Original DSP56800 Code                                     | 4-3  |

|-------------------|------------------------------------------------------------|------|

| Code Example 4-2  | Same Code Mapped to DSP56800E                              | 4-3  |

| Code Example 4-3  | Original DSP56800 Code                                     | 4-4  |

| Code Example 4-4  | Correct Execution on DSP56800E Architecture                | 4-4  |

| Code Example 4-5  | Correct DSP56800E Execution if no AGU overflow/underflow   | 4-4  |

| Code Example 4-6  | Original DSP56800 Code                                     | 4-5  |

| Code Example 4-7  | Correct Execution on DSP56800E Sequence                    | 4-5  |

| Code Example 4-8  | Original DSP56800 Code                                     | 4-6  |

| Code Example 4-9  | Original Code Mapped to DSP56800E Syntax                   | 4-6  |

| Code Example 4-10 | Breaking Up the Original Sequence To Correct Overflow      | 4-6  |

| Code Example 5-1  | Original DSP56800 Code                                     | 5-2  |

| Code Example 5-2  | Dependency after a Tcc Instruction with R0 Modification    | 5-5  |

| Code Example 5-3  | Dependency after a Tcc Instruction with R0 Modification    | 5-5  |

| Code Example 5-4  | Assembling Sequence with AGU Dependency                    | 5-5  |

| Code Example 5-5  | Assembling Sequence with AGU Dependency                    | 5-5  |

| Code Example 5-6  | Loading Pointer with Immediate Data                        | 5-8  |

| Code Example 5-7  | Loading Pointer with 16-bit Value                          | 5-8  |

| Code Example 5-8  | Loading Pointer from Register or Memory                    | 5-8  |

| Code Example 5-9  | Mixed Instructions & Loading Pointers w/ Offset Value      | 5-9  |

| Code Example 5-10 | Copying a 13-bit Value from the LC Register—DSP56800       | 5-10 |

| Code Example 5-11 | Copying a 13-bit Value from the LC Register—DSP56800E      | 5-10 |

| Code Example 5-12 | Emulating Saturation with ADC Instruction                  | 5-13 |

| Code Example 5-13 | Emulating Saturation with SBC Instruction                  | 5-13 |

| Code Example 5-14 | Emulating Saturation with DIV Instruction                  | 5-13 |

| Code Example 5-15 | Difficult Case—Repeat Looping with SA set                  | 5-13 |

| Code Example 5-16 | Entering Data-Memory Execution Mode, 19-Bit Target Address | 5-15 |

| Code Example 5-17 | Exiting Data-Memory Execution Mode, 19-Bit Target Address  | 5-16 |

| Code Example 5-18 | Unsupported DSP56800 LEA Instruction Syntax                | 5-17 |

| Code Example 5-19 | Correct DSP56800 LEA Instruction Syntax                    | 5-17 |

| Code Example 5-20 | Full Context Save for DSP56800E                            | 5-19 |

| Code Example 5-21 | Full Context Restore for DSP56800E                         | 5-20 |

| Code Example 5-22 | Enabling Interrupts for DSP56800E - Setting CCPL to "0"    | 5-23 |

| Code Example 5-23 | Enabling Interrupts for DSP56800               | 5-23 |

|-------------------|------------------------------------------------|------|

| Code Example 5-24 | Demonstrating Delay after Enabling Interrupts  | 5-23 |

| Code Example 5-25 | Disabling Interrupts - Setting CCPL to "3"     | 5-24 |

| Code Example 5-26 | Demonstrating Delay after Disabling Interrupts | 5-24 |

# **Chapter 1 Introduction**

The DSP56800E is designed to enhance the combined MCU/DSC functionality of its predecessor, the DSP56800. The new architecture has been developed to ensure that programs originally written for the DSP56800 (also referred to as legacy code) will assemble and run correctly through the porting process. This process can be guaranteed by adopting a number of simple rules described in this guide. The CodeWarrior Assembler (CW) available from Metrowerks, also provides messages designed to facilitate the porting process.

The complete instruction set of the DSP56800 is supported by the toolset available for the DSP56800E. Assembly code developed for the DSP56800 can be directly interpreted by the CW Assembler when the option to allow legacy instructions is set. When this mode of operation is enabled, the assembler is configured to recognize the DSP56800 as well as DSP56800E syntax. Consequently, the original source code generally does not have to be translated to the new DSP56800E syntax unless the user wants to optimize the code for performance and code density. Debugging assembly files under CodeWarrior is also done on the original syntax.

The new architecture also introduces additional addressing modes and instructions for the expressed purpose of supporting legacy DSP56800 instructions LEA, TSTW, and MOVE. This added capability is not described in the *DSP56800E Core Reference Manual*; it is only documented in this guide. These special legacy instructions are only preserved in the 56800E's architecture to guarantee exact execution of legacy code. The legacy instructions appear shaded in Table A-10 page A-8 to specifically highlight their use in this architecture.

Similarly, there are some differences in instruction syntax between the DSP56800 and DSP56800E architectures which are shown throughout the guide. The exact mnemonic mapping of each DSP56800 instruction into the corresponding DSP56800E assembly instruction is also shown in Table A-10 through Table A-14. In some cases, the mapping requires an adjustment, as is the case when loading the N register, (see Note 1 at the end of Table A-10), or when replacing REP LC with the DOSLC instruction.

This guide discusses all porting issues between the DSP56800 and the DSP56800E. It illustrates and examines architectural differences, discusses all compatibility issues between the two architectures, and provides assembly code segments which demonstrate how compatibility can be achieved with minimal user intervention on the original legacy code.

## **Using This Document**

This document provides a guide for porting legacy DSP56800 code to execute in the DSP56800E core. It is organized to provide the following information:

- Quick reference on compatibility issues, page 2-1

- Summary of the architectural extensions in the DSP56800E, page 3-1

- Programming model comparison, page 3-2

- Memory model comparison, page 3-4

- AGU registers, page 4-1

- Compatibility issues, page 5-1

- Tuning ported code for performance, page 6-1

- Mapping tables from DSP56800 to DSP56800E architecture, page A-8

#### Running DSP56800 Code on the DSP56800E

To use this document efficiently, the user should read Chapter 2, "Quick Reference". Chapter 2 presents a summary of all compatibility issues that may arise during the porting process, and provides a list of recommendations for producing upward-compatible code for the DSP56800.

#### **Understanding Architectural Differences**

To understand the architectural differences between the DSP56800 and the DSP56800E, users should familiarize themselves with Chapter 3, "Comparing the Two Architectures". This chapter introduces the extended features of the DSP56800E that enhance performance and improve program code density. Further information on DSP56800E architecture can be found in the *DSP56800E Core Reference Manual*.

### **Tuning Ported Code**

Once the code has been assembled correctly, the user can refer to Chapter 6, "Optimizing Legacy Code" for hints on optimizing performance and reducing code density. Chapter 6 does not provide a complete discussion of this issue because it is dependent on the application and programming style.

# Chapter 2 Quick Reference

This chapter summarizes the compatibility issues that can arise between the DSP56800 and DSP56800E and offers a list of recommendations for producing DSP56800 that is compatible with the DSP56800E.

## 2.1 Compatibility Issues

This section provides a quick reference list of possible compatibility issues between the DSP56800 and DSP56800E.

- 1. Section 2.1.1 lists all cases that require immediate user intervention.

- 2. Section 2.1.2 on page 2-4 presents uncommon cases where intervention is not immediately required.

- 3. Section 2.1.3 on page 2-6 covers cases where intervention is not needed.

- 4. Section 2.1.4 on page 2-7 describes cases that may arise when both syntax are used together.

All items are cross-referenced with their detailed discussion in Chapter 5, "Compatibility Issues."

### 2.1.1 Intervention Required

The compatibility issues summarized in Table 2-1 include all cases which may require some intervention from the user. In some cases the mapping of the assembler will generate the desired behavior. But in cases where the programming style is incompatible with the new architecture, the user may be required to make some minor adjustments to the legacy code, e.g. replacing numerical targets with labels, or sign extending the N register when its actually used as an offset (rather than a pointer).

Table 2-1. Cases With User-Intervention Requirements

| Case |                         | Descriptions                                                                                                                                                                                                                                      |

|------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI-1 | Jcc<br>JSR<br>JMP<br>DO | <numerical_absolute_address> <numerical_absolute_address> <numerical_absolute_address> <source/>,<numerical_absolute_address></numerical_absolute_address></numerical_absolute_address></numerical_absolute_address></numerical_absolute_address> |

|      |                         | ler requires labels for Absolute target addresses. Guarantees correct operation in cases ode growth occurs and intended target moves. Refer to Section 5.9 on page 5–10.                                                                          |

Table 2-1. Cases With User-Intervention Requirements (Continued)

| Case | Descriptions                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| UI-2 | Bcc *(±) <numerical_relative_offset> (or without the "*")  BRA *(±)<numerical_relative_offset> (or without the "*")  BRCLR #Mask8,<source/>,*(±)<numerical_relative_offset> (or w/o "*")  BRSET #Mask8,<source/>,*(±)<numerical_relative_offset> (or w/o "*")</numerical_relative_offset></numerical_relative_offset></numerical_relative_offset></numerical_relative_offset>                             |  |  |

|      | Assembler requires labels for target addresses. Guarantees correct operation in cases where code growth occurs and intended target moves. Refer to Section 5.9 on page 5–10.                                                                                                                                                                                                                              |  |  |

| UI-3 | Bcc <target_label> BRA <target_label></target_label></target_label>                                                                                                                                                                                                                                                                                                                                       |  |  |

|      | If code growth places the Target_Label beyond the 7-bit offset, a link error will occur; the user must use the forcing operator ">" on the Target_Label to force the assembler to use a branch with an 18-bit offset. Refer to Section 5.4.3 on page 5–6.                                                                                                                                                 |  |  |

| UI-4 | BRCLR #Mask8, <source/> , <target_label> BRSET #Mask8,<source/>,<target_label></target_label></target_label>                                                                                                                                                                                                                                                                                              |  |  |

|      | If code growth places the Target_Label beyond the 7-bit offset, a link error will occur. Only 7-bit offset are available for these instructions. Replace BRCLR with "BFTSTL #MASK16, <source/> " followed by "BCS > <target_label". "bftsth"="" 5.4.3="" 5–6.<="" bcs.="" brset,="" by="" followed="" for="" instruction="" on="" page="" refer="" section="" td="" the="" to="" use=""></target_label".> |  |  |

| UI-5 | DO LA, <end_of_loop_label></end_of_loop_label>                                                                                                                                                                                                                                                                                                                                                            |  |  |

|      | The LA register is no longer supported for this instruction; use an alternate register. Refer to Section 5.10.1 on page 5–11.                                                                                                                                                                                                                                                                             |  |  |

| UI-6 | REP LC                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|      | User must map instruction to DOSLC and insert a single NOP instruction in the loop body to complete the 2-word minimum requirement for DOSLC instruction. Refer to Section 5.10.1 on page 5–11                                                                                                                                                                                                            |  |  |

| UI-7 | REP LA                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|      | The LA register is no longer supported for this instruction; use an alternate register. Refer to Section 5.10.1 on page 5–11.                                                                                                                                                                                                                                                                             |  |  |

| UI-8 | LEA (SP)+N  MOVE X:(SP+N),8-HHHHH  MOVE X:(SP+N),8-SSSS  MOVE 8-DDDDD,X:(SP+N)  TSTW X:(SP+N)                                                                                                                                                                                                                                                                                                             |  |  |

|      | For register indirect addressing modes using both the SP and N registers, the instruction "SXTA.W N" must immediately precede any of the instructions listed above, (to preserve the intended sign). Note: If N is not used as an offset register, no sign extension is required, (the upper 8-bits should be zeroes). Refer to Section 5.4.2 on page 5–5.                                                |  |  |

Table 2-1. Cases With User-Intervention Requirements (Continued)

| Case  | Des                                                                                                                                                                                                                                                                                                                | criptions                                                                                                                                                                                                                                                                                                                       |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI-9  | MOVE <source_register>,X: (Rj+xxxx) MOVE X: (Rj+xxxx),<dest_register> TSTW X: (Rj+xxxx)</dest_register></source_register>                                                                                                                                                                                          | ) (R0 & R1 in modulo addressing only) (R0 & R1 in modulo addressing only) (R0 & R1 in modulo addressing only)                                                                                                                                                                                                                   |

|       | represents the offset, above instructions must b TST.W. When the original xxxx is represented in                                                                                                                                                                                                                   | n hex, it must be sign extended to 32-bits, (e.g. \$FFF8 xxxx represents the base address and Rj the offset,                                                                                                                                                                                                                    |

|       | LEA (Rj+xxxx)                                                                                                                                                                                                                                                                                                      | LEA (Rj+xxxx)                                                                                                                                                                                                                                                                                                                   |

|       | MOVE X:(Rj), < Dest Register>                                                                                                                                                                                                                                                                                      | TSTW X:(Rj)                                                                                                                                                                                                                                                                                                                     |

|       | LEA (Rj-xxxx)                                                                                                                                                                                                                                                                                                      | LEA (Rj-xxxx)                                                                                                                                                                                                                                                                                                                   |

|       | Refer to Section 5.3 on page 5-3.                                                                                                                                                                                                                                                                                  | , <b>,</b>                                                                                                                                                                                                                                                                                                                      |

| UI-10 | New requirements when entering and exiting X/                                                                                                                                                                                                                                                                      | P Mode.                                                                                                                                                                                                                                                                                                                         |

|       | Specific sequence must be followed to switch to (and Refer to Section 5.14 on page 5–14.                                                                                                                                                                                                                           | d return from) executing programs from data memory.                                                                                                                                                                                                                                                                             |

| UI-11 | Compatibility issues at the chip level                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                 |

|       | <ul> <li>must adjust references to the table.</li> <li>The location of the peripheral space is a location of the memory mapped registe chip implementations.</li> <li>The DSP56800E architecture does not off-chip data memory.</li> <li>The DSP56800E core does not define the specific off-chip data.</li> </ul> | not restricted by the core. For exact compatibility, user not restricted by the core. For exact compatibility, the r should be in the exact locations as the DSP56800 restrict the performance of dual read operations on the exact operation of the OMR's EX bit. (When this bit desses to X memory to be from off-chip X data |

| UI-12 | BFCLR #\$0300,SR<br>BFSET #\$0300,SR                                                                                                                                                                                                                                                                               | ; Enable Interrupts<br>; Disable Interrupts                                                                                                                                                                                                                                                                                     |

|       | the interrupt arbiter sees the current core interru<br>instructions in the following 6 clock cycles will b<br>the new CCPL and are taken. Refer to Section                                                                                                                                                         | cution of the BFCLR instruction and the point where pt priority level (CCPL). When interrupts are enabled, e executed before any pending interrupts recognize 5.19.1 on page 5–23.                                                                                                                                              |

|       | the interrupt arbiter masks incoming interrupts.                                                                                                                                                                                                                                                                   | When interrupts are disabled, interrupts can still be during any of the next 5 cycles following the BFSET e 6th clock cycle, form the beginning of a                                                                                                                                                                            |

## 2.1.2 Uncommon Cases: Intervention May Be Required

Table 2-2 lists compatibility issues that are uncommon in application code but may require some intervention.

Table 2-2. Uncommon Cases - May Require User-Intervention

| Case | Descriptions                                                                                                                                                                                                                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UC-1 | REP #xx<br>REP <register></register>                                                                                                                                                                                                                                                                                    |

|      | A number of instructions that are not commonly used in repeat loops can no longer be repeated due to code growth. Instead, a DO loop must be used to replace the REP instruction. Refer to Section 5.10.3 on page 5–12.                                                                                                 |

| UC-2 | MOVE <source/> ,LC                                                                                                                                                                                                                                                                                                      |

|      | The LC register is 13-bits on the DSP56800, but is 16-bits on the DSP56800E. When reading the 56800's 13-bit LC register, the upper 3-bits are always zeroed. If this feature is important in an application, refer to Section 5.8 on page 5–10.                                                                        |

| UC-3 | ADC Y,F SBC Y,F DIV DD,F IMPY <src1>,<src2>,FDD (or IMPY16)</src2></src1>                                                                                                                                                                                                                                               |

|      | These instructions are affected and behave differently when SA = 1. On the DSP56800E, these instructions do not saturate their results even if SA is set. Refer to Section 5.11 on page 5–12.                                                                                                                           |

| UC-4 | DEC F (or DECW) INC F (or INCW)                                                                                                                                                                                                                                                                                         |

|      | These instructions are affected and behave differently when CC (or CM in DSP56800E) = 1when the destination is an accumulator. In the 56800E, the zero condition is calculated using bits [31:16] of the accumulator, whereas the 56800 calculates the zero condition using [31:0]. Refer to Section 5.12 on page 5–14. |

| UC-5 | ADD <source_register>,X:aa ADD <source_register>,X:xxxx ADD <source_register>,X: (SP-xx)</source_register></source_register></source_register>                                                                                                                                                                          |

|      | These instructions are affected when memory is the destination. In the DSP56800E, the carry condition is calculated from bit 31 of the result, whereas in the DSP56800, it is calculated from bit 35 of the result. Refer to Section 5.13 on page 5–14.                                                                 |

Table 2-2. Uncommon Cases - May Require User-Intervention (Continued)

| Case  | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UC-6  | Addressing mode, (R2+xx) removed, (where xx is a 6-bit positive offset):  BFCHG #xxxx, X: (R2+xx)  BFCLR #xxxx, X: (R2+xx)  BFSET #xxxx, X: (R2+xx)  BFTSTH #xxxx, X: (R2+xx)  BFTSTL #xxxx, X: (R2+xx)  BRSET #xxxx, X: (R2+xx)  BRSET #xxxx, X: (R2+xx), <target_label>  BRCLR #xxxx, X: (R2+xx), <target_label>  MOVE #xxxx, X: (R2+xx)  Assembler will map these instructions with the Standard 56800E (Rn+xxxx) addressing mode. An</target_label></target_label> |

|       | additional opcode word is required for these instructions. Address wrapping is not performed. Refer to Section 5.2 on page 5–2.                                                                                                                                                                                                                                                                                                                                        |

| UC-7  | Differences in AGU overflow and underflow, e.g. 64K address wrapping.                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | Address wrapping beyond 64K word boundary is not recommended and it is considered a flawed non-portable programming style. There are legacy 56800E instructions that guarantees exact behavior when $\{R0,R1,R2,R3\}$ are used in linear addressing mode, but the following modes can be corrected: $(Rn)+, (Rn)-, (Rn)+N, (R2+xx)$ , but $(SP-xx)$ is not supported for address wrapping. Refer to Section 4.2 on page 4–23.                                          |

| UC-8  | Bit Manipulation operations on SR bits [14:10]  BFCHG #7Cxx,SR  BFCLR #7Cxx,SR  BFSET #7Cxx,SR  BFTSTH #7Cxx,SR  BFTSTL #7Cxx,SR  BRSET #7Cxx,SR  BRSET #7Cxx,SR, <target_label>  BRCLR #7Cxx,SR,<target_label></target_label></target_label>                                                                                                                                                                                                                          |

|       | Bitfield operations on bits [14:10] are not permitted on the DSP56800E architecture. These bits represent the upper 5-bits of the PC register. These same bits are reserved on the DSP56800.                                                                                                                                                                                                                                                                           |

| UC-9  | Legacy programs growing beyond the 64K word boundary.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | The use of both DSP56800 and DSP56800E instructions is only supported for applications fitting in 64K word program memory space and 64K word data memory space. Refer to Section 5.17 on page 5–20.                                                                                                                                                                                                                                                                    |

| UC-10 | LEA (Rj)+,Ri  LEA (Rj)-,Ri  LEA (Rj)+N,Ri  LEA (Rj+N,Ri  For Rj = Ri = {R0,R1,R2,R3}                                                                                                                                                                                                                                                                                                                                                                                   |

|       | Unsupported DSP56800 LEA Instruction Syntax. This undocumented syntax may be accepted by the toolset but is not supported by the DSP56800E Specifications. Refer to Section 5.15 on page 5–17.                                                                                                                                                                                                                                                                         |

## 2.1.3 No User Intervention Required

Table 2-3 lists compatibility issues that are handled automatically by the toolset and do not require intervention.

Table 2-3. Other Cases—No User-Intervention Required

| Case | Descriptions                                                                                                                                                                                                                                                                          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NI-1 | DO LC, <end_of_loop_label></end_of_loop_label>                                                                                                                                                                                                                                        |

|      | If the body of the original loop is 1-word of length, the assembler inserts a single NOP instruction in the loop body to complete the 2-word minimum requirement for the DOSLC instruction. The assembler also remaps the instruction to DOSLC. Refer to Section 5.10.1 on page 5–11. |

| NI-2 | Addressing mode, (R2+xx) removed, (where xx is a 6-bit positive offset):  MOVE X: (R2+xx), 8-HHHH  MOVE 8-HHHH, X: (R2+xx)  TSTW X: (R2+xx)  LEA (R2+xx)                                                                                                                              |

|      | Assembler will map these instructions with the Legacy 56800E (Rn+xxx) addressing mode. An additional opcode word is required for these instructions. Address wrapping is performed. Refer to Section 5.2 on page 5–2.                                                                 |

| NI-3 | ADD X:aa,FDD SUB X:aa,FDD CMP X:aa,FDD DECW X:aa INCW X:aa MOVE X:(SP-xx),F1 MOVE F,X:(SP-xx) MOVE #xx,Rj (with immediate value between [-64,-1]) MOVE #xx,F1 All Instructions using the (R2+xx) addressing mode.                                                                     |

|      | These DSP56800 instructions are automatically mapped to the 56800E equivalent with one extra instruction word. Refer to Section 5.4.5 on page 5–7.                                                                                                                                    |

| NI-4 | LSLL Y1,X0,DD LSLL Y0,X0,DD LSLL Y1,Y0,DD LSLL Y0,Y0,DD LSLL A1,Y0,DD LSLL B1,Y1,DD ASL DD CLR {X0, Y1, Y0, A1, B1, R0-R3, or N} POP 8-DDDDD POP All Instructions above are aliases that were originally mapped to 56800 instructions.                                                |

|      | In all the above cases, the DSP56800E assembler will correctly recognize and map the instruction to its equivalent. Refer to Section A.4, "DSP56800 Instruction Aliases," on page A-25.                                                                                               |

## 2.1.4 Mixed 56800 & 56800E Instructions

Table 2-4 lists compatibility issues that result from mixing syntax from both architectures in an attempt to optimize for performance and code density.

Table 2-4. Mixed DSP56800 & DSP56800E Syntax

| Case | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MX-1 | Sign Extension Requirements for {R0-R3, N} when mixing with 56800E instructions                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | AGU load instructions are mostly mapped to MOVEU. W. This ensures that the upper 8 bits are zeroes, which correctly maps the nature of address values in the 56800. However, when the value in the register represents an offset and code is mixed with 56800E instructions, then sign extension may be required. Refer to Section 5.7 on page 5–9.                                                                                                                                                                       |

| MX-2 | MOVE <source_register>,X: (SP) + MOVE X: (SP) -,<source_register></source_register></source_register>                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | If legacy code is mixed with new DSP56800E instructions and MOVE. L is used to push and pop from the stack (to optimize for performance and codesize), the SP must always remain odd-aligned. In this scenario, if a long move is used and SP is even, a misaligned data access non-maskable interrupt is generated. There is no issue when porting DSP56800 instructions only. Refer to Section 5.16 on page 5–17.                                                                                                       |

| MX-3 | New requirements in stack pointer alignment (in Mixed code only).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | Long moves must always point to the even address (where the lower 16-bits are stored), except when the stack is accessed. If legacy code is upgraded to use long moves, proper care must be taken to keep SP odd-aligned. Refer to Section 5.16 on page 5–17.                                                                                                                                                                                                                                                             |

| MX-4 | New requirements in context save and restore.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | When storing registers in the DSP56800E, care must be taken when storing LC and HWS. The following rules must be followed:  1. If LC must be stored, store LC2 before LC to guarantee restoration of LC2.  2. If HWS must be stored, store SR and OMR before HWS.  3. When storing HWS, two stores are required to store HWS0 followed by HWS1.  4. When storing 36-bits accumulator with MOVE.L, store extension register first. (Rules 2 & 3 are also recommended in the DSP56800). Refer to Section 5.16 on page 5–17. |

## 2.2 Coding Recommendations

The following is a list of recommendations for writing DSP56800 programs that are compatible with the DSP56800E

- Applications should be written so that there is no AGU overflow or underflow over 64K boundaries when accessing data or program memory.

- Do not use program memory space above 64K. For applications that need more than 64K words, it is necessary to use the DSP56800E instruction set only.

- Address wrapping with the stack pointer is not permitted.

- Interpretation of use for AGU registers is important. If an AGU register is used as an offset, it requires a 24-bit signed value. If it represents a pointer, the upper 8-bits must be zeroes.

- Keep the stack pointer odd-aligned when long data elements are stored onto the stack or retrieved from the stack with the MOVE.L instruction.

- Avoid using the DSP56800 instruction aliases (refer to Section A.3 on page A-24).

- Don't set the CC bit in the OMR register; the DSP56800E architecture defines all data types, and condition codes can be set based on the size of the operand.

- Use labels for all branch and jump instructions rather than numerical targets to protect against problems due to growth in code size.

- Do not use an ENDDO instruction in a repeat loop.

- Do not use the information in condition codes updated by the ENDDO instruction.

- In a repeat loop:

- Do not write to the M01 register.

- Do not access the LC register.

- Do not use A1, Y0, A or B1, Y1, B as operands for a multiply, shift, or multiply-accumulate instruction.

- When the recognize-legacy-code switch is set, the assembler automatically selects memory switches to recognize only 64K words of data space and 64K words of program space.

## **Chapter 3**

## **Comparing the Two Architectures**

There are several fundamental changes to the architecture which are useful to understand in the porting process:

- The AGU registers and the AGU arithmetic units have grown from 16 to 24 bits.

- The program memory space has expanded to 4MB.

- The data memory space has grown to 32MB.

- Mapping of some DSP56800 instructions to DSP56800E counterparts require one extra instruction word.

- There are some changes to the pipeline.

The following sections summarize the new features of the DSP56800E, including comparisons of the programming model and memory model between the two architectures. For a complete description of each performance enhancing feature, refer to the *DSP56800E Core Reference Manual*.

## 3.1 Extending the DSP56800 Architecture

The DSP56800E core architecture extends Freescale's DSP56800 Family architecture to a new generation. It remains source-code compatible with DSP56800 devices and adds the following new features:

- Byte and long data types, supplementing the DSP56800's word data type

- 24-bit data memory address space

- 21-bit program memory address space

- Three additional 24-bit pointer registers, R4, R5, and N. The N register can function either as an offset register or a pointer register.

- Four shadow registers, including three 24-bit pointer registers and the Modifier register, M01

- A secondary 16-bit offset register to further enhance the dual parallel data ALU instructions

- Two additional 36-bit accumulator registers

- Full-precision integer multiplication

- 32-bit logical and shifting operations

- The second read in a dual read instruction can now access off-chip memory

- Loop count (LC) register extended to 16 bits

- Full support for nested DO looping through additional loop address and loop count registers, LA2 and LC2

- Loop address and hardware stack extended to 24 bits

#### **Comparing the Two Architectures**

- Two additional interrupt priority levels with a software interrupt trap for each level, plus a low priority software trap, SWILP

- Eight stage instruction pipeline, resulting in higher execution throughput

- Enhanced On-Chip Emulation (Enhanced OnCE) with three debugging modes:

- Non-intrusive real-time debugging

- Minimally intrusive real-time debugging

- Breakpoint and step mode (core is halted)

## 3.2 Programming Model Comparison

The programming model of the DSP56800E core is a superset of the programming model of the DSP56800. Figure 3-1 on page 3-3 shows the DSP56800 programming model overlaying the DSP56800E programming model. The shaded areas indicate the extensions on the DSP56800E architecture. These extensions are discussed in this section.

There are some differences to note between the two programming models that may affect currently written legacy code for the DSP56800:

- The loop counter register, LC, is expanded from 13 bits to 16 bits.

- The loop address register, LA, is expanded from 16 bits to 24 bits.

- The pointer registers, R0–R3, are expanded from 16 bits to 24 bits.

- The offset register, N, is expanded from 16 bits to 24 bits. N can also function as a pointer register for instructions using indirect addressing modes.

- The LIFO hardware stack registers, HWS0 and HWS1, (designated as HWS) are expanded from 16 bits to 24 bits.

- The program counter, PC, is expanded from 16 bits to 21 bits.

- The upper 5 bits of the program counter reside in the status register, SR.

There are other differences between the two programming models that will not affect legacy code. The following new resources were not present in the DSP56800 programming model:

- In the address generation unit:

- The AGU register file has two new pointer registers—R4, and R5. In addition, the offset register N can also be used as a pointer register in the DSP56800E.

- N3 is a new offset register that provides additional addressing modes for dual parallel instructions.

- There are 4 new shadow registers—R0, R1, N, and M01. These registers are used during fast interrupt operation. For additional information on fast interrupt operation, refer to Chapter 8, "Program Controller", in the *DSP56800E Core Reference Manual*.

- In the data arithmetic logic unit:

- The DALU register file has two new accumulators: C and D.

- In the program control unit:

- A second loop counter, LC2 and a second loop address register, LA2, have been added to support nested hardware looping

- The FIRA and FISR registers are new resources specifically designed to support fast interrupt operation.

#### **ADDRESS GENERATION UNIT**

Figure 3-1. Programming Model—DSP56800 vs DSP56800E

## 3.3 Memory MAP Comparison

The DSP56800 and DSP56800E both contain dual Harvard architectures with separate program and data memory spaces. The amount of addressable program and data memory is different in each device, as shown in sTable 3-1.

| Architecture | Program Memory  | Data Memory     |

|--------------|-----------------|-----------------|

| DSP56800     | 2 <sup>16</sup> | 2 <sup>16</sup> |

| DSP56800E    | 2 <sup>21</sup> | 2 <sup>24</sup> |

**Table 3-1. Size of Memory Spaces**

## 3.3.1 DSP56800 Memory Map

The DSP56800 memory map is shown in Figure 3-2.

Figure 3-2. DSP56800 Memory Spaces

The DSP56800 program memory map includes the following characteristics:

- Program size is limited to 64K words.

- Data memory space is limited to 64K words.

- The interrupt vector table is fixed (location and size are defined by chip implementation).

- A special peripheral space accessible using the X:<<pp addressing mode is fixed at address \$FFC0-\$FFFF, is limited to 64 words, and is controlled by the chip implementation. (However, peripherals can be located anywhere in the data memory space.)

- The first 64-word block of data memory is accessible using the absolute short addressing mode, X:aa (or X:<aa).

- No data memory address can be calculated that is larger than 64K.

### **3.3.2** DSP56800E Memory Map

The DSP56800E memory map is shown in Figure 3-3.

Figure 3-3. DSP56800E Memory Spaces

The DSP56800E program memory map includes the following characteristics:

- Program size is expanded to 2M words (4MB).

- Data space is expanded to 16M words (32MB).

- The interrupt vector table is relocatable (location and size are defined by chip implementation).

- The special peripheral space is relocatable. It is still limited to 64 contiguous words, with location defined by chip implementation.

- The first 64-word block of data memory is accessible using absolute short addressing mode: X:aa (or X:<aa).

When an application written in DSP56800 program code is translated to the DSP56800E, the new application must fit in the first 64K words of program memory and must only access data memory in the first 64K words of the data memory space. Any growth in program code size must not increase the size of the application above 64K in DSP56800E code. If an application uses both DSP56800 and DSP56800E instructions and no longer fits within 64K, the user must translate the application to the 56800E syntax.

#### **Comparing the Two Architectures**

Two exceptions are allowed in the data space. Both the system stack and the peripheral space can be located anywhere within the 24-bit data space range, with peripheral space defined by the chip implementation.

#### NOTE:

- A compiler can only access the lower 16MB (2<sup>24</sup>) of Data Memory Space.

- The upper 16MB of data memory cannot be accessed with the following instructions:

- all MOVE.BP instructions

- any MOVE.B that uses addressing mode X: (Rn+xxxxx) where xxxxxx represents a base address in the upper 16MB.

# **Chapter 4 AGU Registers**

To translate a program from the DSP56800 to the DSP56800E, special consideration must be given to the initialization and arithmetic operations of the AGU registers.

## 4.1 Initializing AGU Registers

There are several rules that must be followed to ensure compatibility of DSP56800 programs when writing to the Program Control and AGU registers.

- Registers R0–R3, HWS, and LA must be zero extended in bits [23:16] and are written using the MOVEU. W instruction when writing from another register or from memory.

- AGU register N is written using MOVEU.W, zero extending in bits [23:16]. If N is used as an offset register in the (Rj+N) addressing mode, it must be sign extended to 24-bits. (Refer to Section 5.4.2 on page 5–5).

- When legacy and new instructions are mixed, for any AGU register loaded with a 56800 instruction and used in a 56800E instruction, it is imperative to use either SXTA.W or ZXTA.W to get the intended sign extension. Whenever an AGU is used as an offset, the upper 8 bits must be loaded with the sign value using SXTA.W. When an AGU is used as a pointer, the upper 8 bits must be zeroes. This can be done using ZXTA.W. Refer to Section 5.7 on page 5–9.

- When immediate data is written to AGU registers R0–R3 and N:

- Use "MOVE.W #xx, HHHH" to destination R0–R3, for values xx inside the range [0, 63].

- Use "MOVEU.W #xxxx, SSSS" to destination R0–R3, for values xxxx outside the range [0, 63].

- Use "MOVE.W #xx, HHHH" to destination N, for values of xx inside the range [-64, 63].

- Use "MOVEU.W #xxxx, SSSS" to destination N, for values of xxxx outside the range [-64, 63]. If N is used as an offset, follow this instruction with "SXTA.W N" to preserve the intended 24-bit sign value.

- When immediate data is written to the HWS and LA registers:

- Use "MOVEU.W #xxxx, SSSS" for all values of xxxx

For register field definitions HHHH and SSSS, refer to Table A-5 on page A-3 and Table A-8 on page A-5.

#### 4.2 Issues with AGU Arithmetic

#### NOTE:

It is very rare that a program is written in a manner where the AGU registers are expected to overflow (or underflow). If it is necessary to guarantee correctness even for this unusual coding style, then this section will be useful; otherwise, this section can be bypassed.

A compatibility issue can arise due to the 16-bit width of the DSP56800's AGU registers, address buses, and datapath. The problem occurs when an AGU computation overflows the DSP56800's highest possible address (\$00FFFF) or underflows the lowest possible address (\$000000). This can occur during an effective address calculation or address register update via one of the post-update addressing modes for any of the following DSP56800 instructions:

- Data ALU arithmetic or bit manipulation instructions with one operand in memory

- Move instructions

- Single and dual parallel move instructions

- TSTW (not mapped to the legacy 56800E instruction)

The problem also occurs for AGU calculations using the DSP56800's LEA instruction. Two examples of AGU calculations in Table 4-1 demonstrate this problem.

| Example Calculation | DSP56800 Result<br>(16-bit AGU Arithmetic) | DSP56800E Result<br>(24-bit AGU Arithmetic) | Comments      |

|---------------------|--------------------------------------------|---------------------------------------------|---------------|

| \$00FFFC + \$000010 | \$0000C                                    | \$01000C                                    | AGU Overflow  |

| \$000003 - \$000007 | \$00FFFC                                   | \$FFFFC                                     | AGU Underflow |

Table 4-1. Demonstrating DSP56800 AGU Overflow and Underflow

#### NOTE:

It is not good programming practice to write application code that depends on the wrapping effect of an overflow from 64K to 0 or an underflow from 0 to 64K (i.e., the natural modulo effect on 16-bit AGU registers). Nevertheless, most code written in this matter is covered by special legacy instructions that are defined to emulate the wrapping behavior from the DSP56800 architecture (see Section 5.1 on page 5–1). However, a few cases are not covered by these legacy instructions. Refer to Section 4.2.4 on page 4–5.

Four different techniques discussed in the following sections are used on the DSP56800E architecture to address this problem:

- Cases solved with legacy instructions when using linear addressing

- Cases solved by careful instruction definition

- Cases solved by adding a zero-extend instruction

- Cases not handled by special legacy instructions that can be broken into more than one instruction sequence

# 4.2.1 Cases Solved by Legacy Instructions—Linear Addressing

When linear addressing is used, address wrapping on the DSP56800 16-bit AGU registers R0–R3 is exactly reproduced on the DSP56800E by using the following special legacy instructions:

```

MOVE

X: (Rj+xxxx), DDDDD

MOVE

DDDDD, X: (Rj+xxxx)

MOVE

X: (Rj+N), DDDDD

MOVE

DDDDD, X: (Rj+N)

LEA

(Rj + xxxx)

T.F.A

(Rj)+N

TSTW

X: (Rj + xxxx)

TSTW

X: (Rj+N)

```

Consider the DSP56800 code shown in Code Example 4-1.

#### Code Example 4-1. Original DSP56800 Code

| MOVE | #\$C000,R0  | ; Load 16-bit pointer with \$C000 |

|------|-------------|-----------------------------------|

| LEA  | (R0+\$8000) | ; Add \$8000 to this value        |

The calculated effective address is \$4000. When this code is directly executed on the DSP56800E architecture, it is executed as the two instructions in Code Example 4-2.

#### Code Example 4-2. Same Code Mapped to DSP56800E

| MOVEU.W | #\$C000,R0  | ; Load 24-bit pointer with \$00C000 |

|---------|-------------|-------------------------------------|

| LEA     | (R0+\$8000) | ; Add \$8000 to this value          |

If the effective address were calculated using the normal 24-bit modulo arithmetic of the DSP56800E, the result would be \$014000 rather than the original result of \$4000. However, the calculated result is actually \$004000, the same value generated on the DSP56800. This is because the legacy instructions LEA, MOVE, and TSTW utilize special addressing modes that perform 16-bit AGU arithmetic by zeroing the upper 8 bits of the 24-bit result. These special instructions are shown in the shaded areas in Table A-10 on page A-8.

#### NOTE:

The DSP56800E architecture does not support address wrapping for the SP register, which only uses 24-bit arithmetic. Thus, the legacy instructions do not apply to the stack pointer.

### 4.2.2 Cases Solved by Definition of Operation

In some cases, the definition of an operation helps ensure DSP56800 compatibility. In this case there is no compatibility issue.

Consider the DSP56800 code shown in Code Example 4-3.

#### Code Example 4-3. Original DSP56800 Code

```

MOVE #$1004,R0 ; Load 16-bit pointer with $1004

MOVE #$-4,X0 ; Load negative 16-bit value in X0 ($FFFC)

MOVE X0,N ; Load N with negative value from X0 reg

MOVE X:(R0)+N,X0 ; Updates R0 with -4 ($FFFC)

```

On the DSP56800 architecture, the result in the R0 register after this code sequence is \$1000 due to its 16-bit AGU unit. The '1' located in bit 17 on DSP56800E is not available on the DSP56800 architecture due to its 16-bit datapath. This is shown in Code Example 4-4.

#### Code Example 4-4. Correct Execution on DSP56800E Architecture

```

MOVEU.W #$1004,R0 ; Load 16-bit pointer with $001004

MOVEU.W #$-4,X0 ; Load negative value into X0 ($FFFC)

MOVEU.W X0,N ; Loads N w/ positive value ($00FFFC)

; (MOVEU.W instruction zero extends value)

MOVE.W X:(R0)+N,X0 ; Updates R0 with $FFFFFC, not $00FFFC

; (due to the defn of (Rn)+N addr mode)

```

On the DSP56800E architecture, there should be a problem because the 24-bit N register does not contain a negative value but instead contains a large positive value, \$00FFFC). The result in the R0 register after this code sequence, however, is also \$1000, identical to the result calculated on the DSP56800. The reason that the DSP56800 provides the correct answer is due to the fact that the (Rn) +N addressing mode is defined as a 16-bit address computation. This addressing mode ignores the upper 8 bits of the N register and sign extends from bit 15 before performing the addition. Thus, both architectures update R0 using the value \$FFFFFC and both calculate identical results.

## 4.2.3 Cases Solved by Adding a Zero-Extend Instruction

In most cases, AGU overflow and underflow compatibility issues are directly handled by the assembler by mapping these instructions with their legacy counterparts in the DSP56800E instruction set. Code Example 4-6 demonstrates DSP56800 code where this is the case.

#### Code Example 4-5. Correct DSP56800E Execution if no AGU overflow/underflow

```

MOVEU.W #$F000,R0 ; Load 16-bit pointer with $F000

MOVEU.W #$0004,N ; Load $0004 into the N register

NOP

ADD X0,A X:(R0)+N,X0 ; R0 = $F000 + $0004 = $F004

; on the DSP56800E

; (no AGU overflow occurs)

```

Compatibility issues arise for the X: (Rn) +N addressing mode if it is used in a manner where it overflows the value \$00FFFF or underflows the value \$0000 boundary, such as in Code Example 4-6.

#### Code Example 4-6. Original DSP56800 Code

```

MOVE #$F000,R0 ; Load 16-bit pointer with $F000

MOVE #$2000,N ; Load $2000 into the N register

NOP ;

ADD X0,A X:(R0)+N,X0; R0 = $F000 + $2000 = $1000 on DSP56800

; (AGU overflow occurred - 16-bit ALU)

```

One solution to this problem is to correct the AGU register after the post update with the zero extension instruction ZXTA. W, as shown in Code Example 4-7.

#### Code Example 4-7. Correct Execution on DSP56800E Sequence

```

MOVEU.W #$F000,R0 ; Load 16-bit pointer with $F000

MOVEU.W #$2000,N ; Load $2000 into the N register

NOP ;

ADD X0,A X:(R0)+N,X0 ; R0 = $00F000 + $002000 = $011000

ZXTA.W R0 ; R0 is corrected by zero extending

; the upper 8-bits on R0

```

Another solution is to break the original DSP56800 parallel instruction into separate DSP56800E instructions, as discussed in the next section. Breaking the instruction avoids the overflow (or underflow), while the zero-extension method corrects the result after the overflow.

The following addressing mode cases are not handled by special legacy instructions. They can also be corrected after the overflow (or underflow) takes place by adding the zero-extension instruction, "ZXTA.W Rk" after the post-update of Rk.

- (Rk)+

- (Rk)-

- (Rk)+N

If it is known that there is no AGU overflow or underflow in an application and it is important to maintain peak performance, it is not necessary to zero extend or break the original DSP56800 instruction.

## 4.2.4 Cases Solved by Breaking Into More Than One Instruction

There are some cases of AGU overflow or underflow that are not solved by the legacy instructions or the definitions of the operations. The following addressing modes are subject to compatibility mismatch on overflow or underflow:

- Cases that can also be corrected by adding the zero-extension instruction, "ZXTA.W Rk" (see Section 4.2.3 on page 4–4):

- -- (Rk)+

- (Rk)-

- -- (Rk)+N

- Cases mapped to the DSP56800E standard (Rk+xxxx) addressing mode, (see Section 5.2 on page 5–2 for a complete list of instructions with this addressing mode):

- (R2+xx), when this addressing mode is mapped to the standard mode

Code Example 4-8 demonstrates addressing modes that are subject to compatibility mismatches when the DSP56800's 16-bit AGU register width overflows or underflows.

#### Code Example 4-8. Original DSP56800 Code

| MOVE        | #\$FFFF,R2       | ; Load 16-bit pointer with \$FFFF    |

|-------------|------------------|--------------------------------------|

| MOVE<br>NOP | #\$2000,X:(R2+3) | ; Write \$2000 to location \$0002    |

|             | #\$FF00,X:(R2+5) | ;<br>; Set \$FF00 on location \$0004 |

When the user does not correct this sequence, overflow occurs as shown in Code Example 4-9.

#### Code Example 4-9. Original Code Mapped to DSP56800E Syntax

By partitioning the instruction into two parts, the AGU register can be safely post-updated to avoid the overflow by using the LEA instruction. This is shown in Code Example 4-10.

#### Code Example 4-10. Breaking Up the Original Sequence To Correct Overflow

```

; Load 16-bit pointer with $FFFF

MOVE

#$FFFF,R2

; NEW SEQUENCE

LEA

(R2+3)

; Update R2 with value $0002

#$2000,X:(R2) ; Write $2000 to location $0002

MOVE

LEA

(R2-3)

; Update R2 with value $FFFF

NOP

; NEW SEQUENCE

; Update R2 with value $0004

LEA

(R2+5)

#$FF00,X:(R2); Set $FF00 on location $0004

BFSET

; Update R2 with value $FFFF

LEA

(R2-5)

```

The (SP-xx) addressing mode is also subject to mismatch on overflow or underflow. The DSP56800E architecture does not support wrapping the stack pointer at the \$FFFF boundary. Refer to Section 5.4.2 on page 5–5.

# **Chapter 5 Compatibility Issues**

This section outlines potential assembly language incompatibilities between the DSP56800 and the DSP56800E and provides reference to other places in the document where these cases are discussed in detail. The assembler is designed to select the correct mapping and resolve most of the issues that arise when porting DSP56800 assembly code to the DSP56800E architecture. In other cases, the coding style used on legacy code can affect this process and may require user to map the instruction (or sequence of instructions) manually to ensure correct execution. This document currently covers assembly language issues only; a future revision will also include a section on issues pertaining to porting C-language programs from the DSP56800 to the DSP56800E architecture.

## 5.1 New Special Legacy Instructions

Two new addressing modes are provided for the expressed purpose of matching the 16-bit AGU register widths exactly with key addressing modes found on the DSP56800:

• X: (Rj+N) Indexed by Offset Register N—Legacy Version

• X: (Rj+xxx) Indexed by 16-Bit Displacement—Legacy Version

These addressing modes share a common trait—the upper 8-bits of the address value are forced to zeroes. This refers to the effective address computed by the instruction.

#### NOTE:

It is recommended that the addressing modes in this class not be used in new applications written for the DSP56800E.

This section lists the instructions that make use of these addressing modes. These instructions are found only in this guide and are highlighted in Table A-10 on page A-8. Details on these instructions can be found in section Section A.3, "Legacy Instruction Summary Tables," on page A-24. With no exceptions, the following list is only applicable for AGU registers R0, R1, R2 and R3. In cases where the original instruction uses these two modes with the stack pointer, SP, the mapping table utilizes the standard DSP56800E translation. To illustrate this, Code Example 5-1 shows how "LEA (R0)+N" and "LEA (SP)+N" are mapped.

#### Code Example 5-1. Original DSP56800 Code

```

;Demonstrating Legacy Mapping on LEA for R0 and SP

8420 LEA (R0)+N ; mapped to LEA (R0)+N

89BB LEA (SP)+N ; mapped to ADDA N,SP

89BB ADDA N,SP

```

The following instructions, which appear only in this guide, are characterized by the unique way in which address arithmetic is performed—the upper 8-bits of the 24-bit AGU register are forced to zeroes to form the effective address of the instruction.

```

LEA

(Rj)+N

- update Rj by N

(N treated as a 16-bit register)

LEA

- update Rj by #xxxx

(Rj + xxxx)

- read value from memory location Rj+xxxx

MOVE

X: (Rj+xxxx), DDDDD

MOVE

X: (Rj+N), DDDDD

read value from memory location Rj+N

MOVE

DDDDD, X: (Rj+xxxx)

write reg value to memory location Rj+xxxx

MOVE

DDDDD, X: (Rj+N)

write reg value to memory location Rj+N

- test value from memory location Rj+xxxx

TSTW

X: (Rj + xxxx)

X: (Rj+N)

- test value from memory location Rj+N

TSTW

```

## 5.2 Replacement of (R2+xx) with (Rj+xxxx)